|

1 引言

随着微电子技术的迅速发展,DDS技术得到了广泛的应用,市场上有很多高性能多功能的DDS专用器件,但其工作方式和控制方式固定,一般用户很难按自己的要求获得相应的波形[1,2]。同时任意波的输入方式目前都只限于时域,无法实现电子、通信等领域的科研与教学中所需频域参数定义的波形。本文介绍一种基于DDS的可视化信号发生器,它高精度地生成双通道±8 V、0.01 Hz~10 MHz正弦波等常规波形。还可产生数码流、调制信号、随机噪声、扫频信号及时域或频域自定义波等信号,信号参数均步进在线可调,由USB1.1与DELPHI7.0完成与PC连机时的接口及图形操作界面设计,TFT实现单机工作时的图形操作界面,实验表明该设计是行之有效的。

2 系统设计

系统结构框图如图1所示,其中用DELPHI来开发图形上位机软件;PDIUSBD12为USB控制器,MCU实现系统智能控制和数值运算,FPGA为系统数字载体,内建DDS、MCU接口、时钟控制、Flash读写、键盘扫描和TFT控制等模块。设计双路D/A输出通道,通过调节DAC参考电压提高小信号幅度分辨率,系统既可由上位机软件控制实现信号源功能,也可通过触摸按键和TFT图形液晶显示器智能实现便携式任意源功能。

设计中取系统时标信号频率为fr=100 MHz,输出信号每一周期由N个取样点构成,取样周期为Tr=(1/fr),则输出信号的频率为fo=fr/N,设合成信号初相为ψ0,相位累加器位数为x=32,存储器位数为y=10,则

其中,f0min为合成器最低输出频率,△f为频率分辨率,设输出频率控制字为k,则:

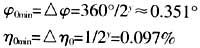

nψ=ψ02x/2πk为初相量化值,最小相移、占空比的最小值和分辨率分别为:

当x-y>4时,正弦输出相位截断噪声的信噪比SNRP=6.02y-3.992=68.24dB[1,3],可见相位截断后仍有较高的信躁比,幅度噪声的信噪比SNRE=6.02y+20lgr,其中r为输出波形与满刻度的峰-峰值之比,取r=1,则SNRE=72.2 dB[3,4]。

3 FPGA与分段时标设计

FPGA设计原理如图2所示。DDSA、DDSB均是双通道DDS产生模块,内部由32位累加器和波形存储器RAM组成,累加器在累加时钟的控制下对频率控制字k进行累加,其结果作为波形存储器RAM的地址来读出RAM中波形数值。波形存储器RAM为双口RAM,既可在读信号、读地址的配合下进行RAM的读操作。也可在写信号、写地址和数据输入信号的配合下进行写操作,更换波形数据见图3。双通道设计为互相调制提供了方便。波形存储器RAM为双口RAM,在进行波形切换时,由MCU控制FPGA启动Flash读写单元,以10 MHz的速度从外部的Flash中读取4 096个波形数据到双口RAM中。

|